2021年,TSMC在Hotchips会议上公布过其硅光封装路线,具体可参见小豆芽的这篇笔记TSMC的硅光封装路线。时隔两年,在今年的ECTC会议上,台积电展示了其最新的硅光封装路线图,小豆芽这里整理下相关细节,供大家参考。

两年前的硅光平台称为COUPE(Compact Universal Photonic Engine),现在已经升级成COUPE 2.0, 主要更新有两点: 1)EIC与PIC之间的电互联采用混合键合技术 TSMC列出了光电集成系统的几种封装方案,并进行了对比,如下图所示,

(图片来自文献1)

对于单片集成方案,EIC与PIC采用相同工艺节点,限制了其EIC性能的进一步提升。对于wirebonding和micro-bump这两种封装方案,从长远角度看,随着带宽需求的持续提升,wire和bump寄生参数的影响无法消除, 互联密度也无法继续提高,会限制系统性能的进一步提升。台积电将混合键合(hybrid bonding)的技术引入到COUPE2.0中,信号通过TSV进行垂直互联,PIC与EIC中间不再存在micro-bump,没有空隙,将寄生参数最小化,从而带来功耗与性能的提升。

Hybrid bonding技术,也称为DBI技术,即direct bonding interconnect, 芯片间不再通过bump互联。两片wafer在室温下通过氧化物的分子间作用力附着在一起,再通过升温退火,铜发生膨胀并牢固地键合在一起,从而形成电连接。台积电的混合键合技术也称为SoIC (System on Integrated Circuit), 是其3dFabric封装平台中的一个重要技术。混合键合技术可以实现更高密度的电互联,其pitch可以小于20um。由于两片wafer间没有空隙,寄生参数非常小,可以支持更大的带宽。

(图片来自https://semiengineering.com/hybrid-bonding-basics-what-is-hybrid-bonding/)

2)与微透镜结合的宽带光栅耦合器 在COUPE2.0中,台积电研发了一种宽带光栅耦合器,兼顾了光栅耦合器的灵活性以及边缘耦合器宽带工作的优势,其耦合损耗为0.3dB,对准容差为±10um,结合微透镜,对准容差可以扩大至±20um。其示意图如下图所示。

(图片来自文献1)

台积电文章中没有给出具体的器件设计细节或者仿真与实测的光谱图,此处存疑。从台积电最新的专利中可以获得一定的信息,其采用了back reflector + microlens的方案,背面的金属反射层增加了耦合效率,而上方的硅微透镜则增加了光栅耦合器的带宽。下图中107为光栅耦合器,145为金属反射层,131为微透镜。

(图片来自文献2)

将OE模块与不同功能的电芯片封装在一起,形成广义的CPO, 如下图所示。A图为狭义的CPO光模块,OE模块分布在交换芯片的四周,金属互连线的距离得以缩小,从而降低功耗。B/C/D图中计算芯粒、存储芯粒和OE模块封装在一起,信号通过OE模块传输到另一颗芯片处,实现芯片间的光互连(inter-package optical IO),进一步可实现资源的解耦,扩展HPC的算力。D/E图中,每一个计算和存储芯粒附带一个OE模块,不同芯粒间通过OE模块实现芯片内信号的互联(intra-package interconnection network),此时不同OE模块需通过interposer中的光波导实现较长距离的光信号连接,构成芯片内的光互联网络。与图BCD类似,整个芯片还通过单独的一个OE模块与其他芯片互联。

(图片来自文献1)

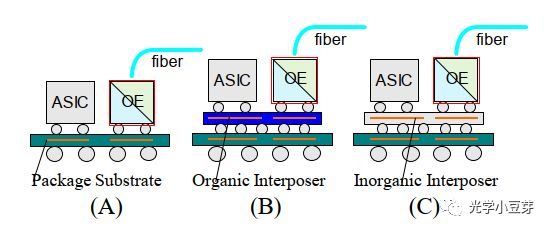

TSMC将带有光波导互联、电信号互联两重功能的interposer称为Composite Interposer(CI), 对应的硅光封装平台也称为iOIS_CI。CPO的封装根据所采用的substrate与interposer,可以分为三类,即MCM, organic interposer, inorganic interposer, 如下图所示。

(图片来自文献1)

MCM方案比较常见,ASIC芯片和OE模块分别flip-chip到substrate上,肩并肩地分布,利用substrate中的铜线实现两颗芯片的电互联。该方案受限于金属互连线的特征尺寸,信号带宽和带宽密度无法进一步提升。Organic Interposer方案中,ASIC芯片和OE模块首先flip-chip到有机interposer上,然后interposer再与substrate互联。Organic interposer中可以实现更高密度的电互联,RDL的特征尺寸为2/2um,其对应TSMC的INFO_oS封装平台。而Inorganic interposer方案,则将interposer替换成非有机材料,例如硅基interposer, 其金属的特征尺寸可以降低到0.4/0.4um,进一步提高信号互联的带宽密度,其对应TSMC的CoWoS_S封装平台。三种方案的性能比较,如下表所示。CI方案在各方面的性能都占优,但是工艺挑战也非常大,成本较高。

(表格来自文献1)

由于CI方案的成本较高,TSMC也提出了硅桥接(silicon bridge, 也称为local silicon interconnection )的方案,如下图所示, 在substrate或者organic interposer局部提供高密度的金属互联,既满足了高密度互联的需求,也降低了成本。这两种方案对应TSMC的Info_LSI和CoWoS_L封装方案。

(图片来自文献1)

针对不同的应用场景,TSMC分别罗列了相应的封装方案。对于计算和存储芯片在同一个package中的情形,计算芯片与存储芯片的距离非常近,并且需要高速交换数据,两者被放置在同一个inorganic interposer上,形成存算一体的module,如下图所示。A图为Compute-Memory模块与OE模块通过MCM的封装形式,B图为organic interposer的封装方案,C图和D图为inorganic interposer的方案,D图中MEM/Comp/OE芯片并排放置在同一个interposer上。

(图片来自文献1)

类似的,为了降低封装成本,也可以采用桥接的方案,如下图所示。这里就不一一介绍了,与前面方案的差别是在substrate和organic interposer中引入硅桥连接。

(图片来自文献1)

PIC自身也可以作为interposer, 利用金属互联和TSV分别实现水平和竖直方向的电互联,如下图所示。其中A图为普遍的封装形式,ASIC芯片和OE芯片放置在PIC interposer上,B图中MEM-Comp模块和OE模块放置在PIC上,C/D/E中将OE模块替换成其它的EIC。

(图片来自文献1)

对于单片集成的硅光平台,也可以采用类似的封装方案,由于PIC和EIC是合体的,对应的封装方案看起来更加简洁,如下图所示。A图中ASIC芯片flip-chip到单片集成的OE芯片上,B图中ASIC芯片替换成MEM和Comp芯片。

(图片来自文献1)

上述的讨论中,无论是MCM, organic还是inorganic interposer方案,主要强调的是电互联,光信号只存在于OE模块处。TSMC的CI封装方案中,interposer中既包含电连接,也包含光连接。在Interposer中加工低损耗的光波导,通过多层波导耦合结构,实现了OE模块与CI波导之间的低损耗光连接。光波导的典型参数如下表所示,波导的传输损耗为0.21dB/cm, 不同层波导的转移损耗为0.015dB, 带宽密度可以达到44.9Tbps/mm。

(表格来自文献1)

基于该OE-CI封装方案,可以对硅光封装平台进行进一步的拓展,将激光器、SOA、APD、LNOI等光电芯片也混合集成到CI上,利用CI进行光信号的传播,实现更多的功能,如下图所示。

(图片来自文献1)

以上是对台积电的硅光封装平台iOIS的介绍,其主要包含两部分,COUPE2.0和CI平台。相比于初代硅光平台,COUPE2.0中采用了hybrid bonding的方案,EIC与PIC的电互联寄生参数进一步缩小,bonding pitch也进一步缩小,有助于实现更高带宽的信号互联。COUPE2.0对光栅耦合器进行了升级,实现了宽带低损耗的光栅耦合器,其耦合损耗只有0.3dB。在CI平台中,加工出多层低损耗光波导结构,同时提供了高密度的电连接与光连接。关于Interposer引入光波导进行光互联,产业界已经有类似的技术探索。

整体说来,台积电利用其强大的3DFabric先进封装平台,将相关的封装技术移植到硅光平台上,包括Info、CoWoS、SoIC等技术,打造了iOIS平台。文章中更多的是封装形式的罗列,EIC/PIC/MEM/Comp等芯片像乐高一样被组装起来。但并未涉及更多的细节,小豆芽猜测应该还处于工艺研发阶段,更多的是该技术方案的展望。让我们拭目以待!借助于iOIS平台,可以实现多颗芯粒在同一个封装内的互联,也可以实现多颗芯片间的高带宽互联。基于此,硅光互联将必将在算力扩展上发挥重要的作用。此外,硅光芯片的一个重要发展趋势是与先进封装技术深度结合,当然这也是一把双刃剑,机遇与挑战并存,先进封装技术的工艺开发与技术积累都需要时间。

文章中如果有任何错误和不严谨之处,还望大家不吝指出,欢迎大家留言讨论。

参考文献

- H. Hsia, et.al., "Integrated Optical Interconnect Systems (iOIS) for Silicon Photonics Applications in HPC", ECTC 2023

- C. Yu,et.al., "Package structure including photonic package and interposer having waveguide", US20230161120A1 US20230161120 S20230161120A1